SiFive's RISC-V cores launch in two SSD families

August 8, 2018 | 11:39

Companies: #fadu #mobiveil #risc-v-foundation #sifive

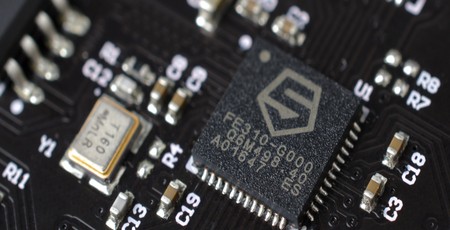

The RISC-V open instruction set architecture (ISA) has scored another pair of big wins this week, with SiFive's core intellectual property (IP) being picked for a pair of high-performance solid-state drive (SSD) families from Mobiveil and Fadu.

Designed to scale from low-power single-core microcontroller implementations to high-performance many-core supercomputers, the RISC-V ISA began life in 2010 at the University of California at Berkeley as a collaborative alternative to proprietary ISAs including x86, Arm, and MIPS. Since reaching a feature-complete state, interest in the ISA for commercial use has been growing: Late last year Western Digital confirmed it would launch RISC-V based data processing products at scale, Nvidia is replacing its in-house RISC-based ISA with RISC-V in its logic controllers, Rambus has launched a RISC-V based security product, and Arm appears to be concerned at the way things are progressing.

At the forefront of this is SiFive, founded by original RISC-V researchers Krste Asanović, Yunsup Lee, and Andrew Waterman and recently the recipient of investment from Intel Capital. It's SiFive's implementations of the RISC-V architecture that have been picked up for use in two new SSD families, replacing proprietary cores in their controllers: Mobiveil's data centre centric FPGA-powered configurable storage family and Fadu's more traditional Bravo family of enterprise SSDs.

While neither company has the name recognition of Western Digital or Seagate, both of whom are working with RISC-V on storage or storage-processing products, they come with considerable praise for the project. 'We chose to partner with SiFive on this SSD platform solution as their cores offer the lowest area and highest power efficiency of any similar cores in the market,' claims Mobiveil chief executive Ravi Thummarukudy, with Fadu's Johyo Lee adding that 'SiFive's RISC-V Core IP was 1/3 the power and 1/3 the area of competing solutions, and gave Fadu the flexibility we needed in optimizing our architecture to achieve these groundbreaking products.'

Mobiveil's implementation sees SiFive's E51 and U54 core IPs added to the company's in-house PCIe, NVMe, LDPC, ONFI, and memory controller IP on a smart reprogrammable storage board aimed at data centre use. Fadu's implementation, meanwhile, uses the E51 core IP alone to build a controller for more traditional SSDs, Annapurna, to first appear in the Bravo enterprise-grade SSD and pushing a claimed 3.5GB/s and 800,000 input/output operations per second (IOPS) performance level at 6-8W of active power.

More information on SiFive's IP can be found on the official website, while the BSD-licensed RISC-V ISA is available from the RISC-V Foundation for anyone to implement, modify, and exploit royalty-free.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.