During his keynote this afternoon, Pat Gelsinger disclosed some more details on Intel’s upcoming Nehalem microarchitecture; this time it was focused on the new power management advancements the architects have made.

With Nehalem, Intel will introduce some more advanced dynamic power management technologies to help to further improve energy efficiency.

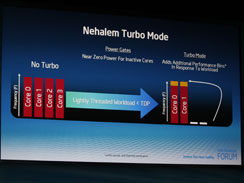

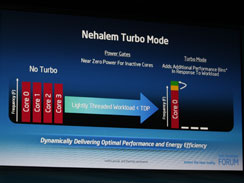

The main focus of his talk on Nehalem today was on Turbo Mode, which basically increases the loaded processing core’s clock speeds and voltages when at least one of the cores is idle in order to deliver the maximum possible performance within the chip’s defined power budget.

Gelsinger invited Rajesh Kumar, Intel Fellow and Director of Circuit and Low Power Technologies, on stage to talk about the technology in a bit more detail.

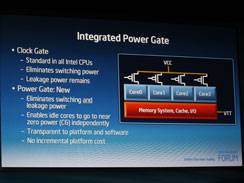

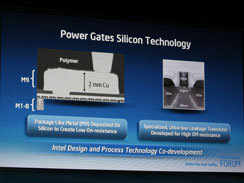

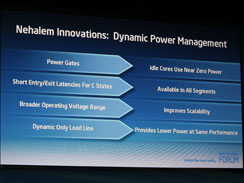

In the past, Intel has clock-gated its chips in order to keep energy efficiency high on the agenda – with Nehalem, Kumar says that in addition to clock gating, processors based on the new microarchitecture will also have power gating capabilities as well.

This will reduce (and potentially eliminate) switching and leakage power, while also allowing idle cores to use nearly zero power by independently entering the C6 power state. Kumar claimed that this will be completely transparent to both the platform and the software running on it, which should mean the benefits are there for all.

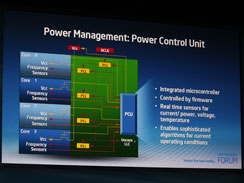

It achieves this by using an integrated microcontroller that Intel calls the Power Control Unit. This part of the Nehalem chip has over one million transistors on its own, which makes it more complex than the original 486 processor, designed by Pat Gelsinger himself.

This all sounds interesting and the final parts of the architecture are being put into place ahead of its launch in a few weeks time. Are you excited to see what level of performance Nehalem will bring to the table? Hopefully we’ll get some preliminary numbers later this week – in the meantime, discuss this new technology in the forums.

With Nehalem, Intel will introduce some more advanced dynamic power management technologies to help to further improve energy efficiency.

The main focus of his talk on Nehalem today was on Turbo Mode, which basically increases the loaded processing core’s clock speeds and voltages when at least one of the cores is idle in order to deliver the maximum possible performance within the chip’s defined power budget.

Gelsinger invited Rajesh Kumar, Intel Fellow and Director of Circuit and Low Power Technologies, on stage to talk about the technology in a bit more detail.

In the past, Intel has clock-gated its chips in order to keep energy efficiency high on the agenda – with Nehalem, Kumar says that in addition to clock gating, processors based on the new microarchitecture will also have power gating capabilities as well.

This will reduce (and potentially eliminate) switching and leakage power, while also allowing idle cores to use nearly zero power by independently entering the C6 power state. Kumar claimed that this will be completely transparent to both the platform and the software running on it, which should mean the benefits are there for all.

It achieves this by using an integrated microcontroller that Intel calls the Power Control Unit. This part of the Nehalem chip has over one million transistors on its own, which makes it more complex than the original 486 processor, designed by Pat Gelsinger himself.

This all sounds interesting and the final parts of the architecture are being put into place ahead of its launch in a few weeks time. Are you excited to see what level of performance Nehalem will bring to the table? Hopefully we’ll get some preliminary numbers later this week – in the meantime, discuss this new technology in the forums.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.