Soft Machines unveils VISC virtual chip architecture

October 24, 2014 | 12:04

Companies: #arm #soft-machines

A multinational late-stage startup has emerged from stealth mode with some dramatic claims for its new microprocessor architecture, VISC, including the promise of a 2-4 times gain in performance over established architectures.

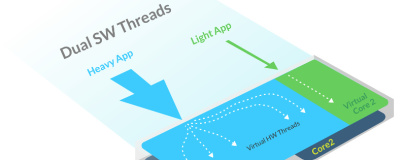

Soft Machines' Virtual Instruction Set Computing (VISC) differentiates itself from established Complex Instruction Set Computing (CISC) and Reduced Instruction Set Computing (RISC) architectures - the most famous examples being x86 and ARM respectively - by doing away with the concept of physical processing cores. Instead, the resources of the chip are made available as 'virtual cores' to 'virtual hardware threads' according to need. The result, the team behind the technology claims, is a boost in instructions per cycle of 3-4 times compared to existing technologies resulting in a 2-4 times boost in performance per watt on both single- and multi-threaded applications.

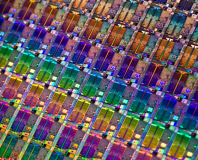

'I believe VISC ushers in the third wave of computer architecture,' boasted Soft Machines co-founder, vice chairman and chief executive Mahesh Lingareddy at the unveiling. 'We've been quietly building the company and developing the VISC architecture for more than seven years. Now that we have working silicon proving the invention, the time to unveil our breakthrough has arrived, and I could not be more excited. We have also proven that you can still build successful semiconductor startup companies and create value with the right vision, technology, team and investors.'

The biggest promise of VISC is in its scalability. The company claims its design can be customised to create everything from low-power devices aimed at the burgeoning Internet of Things (IoT) to high-power processors designed for server use. To prove this, co-founder, president and chief technical officer Mohammad Abdallah has demonstrated a dual-virtual-core VISC system-on-chip prototype at the Linley Processor Conference in Santa Clara which backs up the IPC improvement claims.

'We founded Soft Machines with the mission of reviving microprocessor performance-per-watt scaling. We have done just that with the VISC architecture, marking the start of a new era of CPU designs,' claimed Abdallah. 'CPU scaling was declared dead when the power wall forced CISC- and RISC-based designs into multi-core implementations that require unrealistically complex multi-threading of sequential applications. The VISC architecture solves this problem 'under the hood' by running virtual hardware threads on virtual cores that far exceed the efficiency of software multi-threading.'

With the technology proved in silicon, there remains only one stumbling block: getting software developers to adopt the new architecture. This is the hurdle faced by all new instruction set architectures, and one Soft Machines will need to jump to be in with a chance of survival. Rival chip start-up Adapteva faced similar challenges with its mesh-based Epiphany parallel processing architecture, and drummed up developer interest with a Kickstarter campaign to create a sub-$100 development board featuring a 16-core implementation of its chip; Soft Machines has not yet indicated whether it plans to follow a similar route. It has, however, claimed that an abstraction layer should allow software written for the ARM or x86 instruction sets to run atop a VISC processor while still benefiting from the 2-4x performance boost.

More details on the VISC architecture are available from the Soft Machines website.

Soft Machines' Virtual Instruction Set Computing (VISC) differentiates itself from established Complex Instruction Set Computing (CISC) and Reduced Instruction Set Computing (RISC) architectures - the most famous examples being x86 and ARM respectively - by doing away with the concept of physical processing cores. Instead, the resources of the chip are made available as 'virtual cores' to 'virtual hardware threads' according to need. The result, the team behind the technology claims, is a boost in instructions per cycle of 3-4 times compared to existing technologies resulting in a 2-4 times boost in performance per watt on both single- and multi-threaded applications.

'I believe VISC ushers in the third wave of computer architecture,' boasted Soft Machines co-founder, vice chairman and chief executive Mahesh Lingareddy at the unveiling. 'We've been quietly building the company and developing the VISC architecture for more than seven years. Now that we have working silicon proving the invention, the time to unveil our breakthrough has arrived, and I could not be more excited. We have also proven that you can still build successful semiconductor startup companies and create value with the right vision, technology, team and investors.'

The biggest promise of VISC is in its scalability. The company claims its design can be customised to create everything from low-power devices aimed at the burgeoning Internet of Things (IoT) to high-power processors designed for server use. To prove this, co-founder, president and chief technical officer Mohammad Abdallah has demonstrated a dual-virtual-core VISC system-on-chip prototype at the Linley Processor Conference in Santa Clara which backs up the IPC improvement claims.

'We founded Soft Machines with the mission of reviving microprocessor performance-per-watt scaling. We have done just that with the VISC architecture, marking the start of a new era of CPU designs,' claimed Abdallah. 'CPU scaling was declared dead when the power wall forced CISC- and RISC-based designs into multi-core implementations that require unrealistically complex multi-threading of sequential applications. The VISC architecture solves this problem 'under the hood' by running virtual hardware threads on virtual cores that far exceed the efficiency of software multi-threading.'

With the technology proved in silicon, there remains only one stumbling block: getting software developers to adopt the new architecture. This is the hurdle faced by all new instruction set architectures, and one Soft Machines will need to jump to be in with a chance of survival. Rival chip start-up Adapteva faced similar challenges with its mesh-based Epiphany parallel processing architecture, and drummed up developer interest with a Kickstarter campaign to create a sub-$100 development board featuring a 16-core implementation of its chip; Soft Machines has not yet indicated whether it plans to follow a similar route. It has, however, claimed that an abstraction layer should allow software written for the ARM or x86 instruction sets to run atop a VISC processor while still benefiting from the 2-4x performance boost.

More details on the VISC architecture are available from the Soft Machines website.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.