IBM has announced that it expects to have commercialised its carbon nanotube transistor technology in the early 2020s, thanks to a new design that would allow the transistors to be built on silicon wafers using similar techniques to existing chip manufacturing plants.

The semiconductor industry has been working hard for the last few decades on following Moore's Law, the observation by Intel co-founder Gordon Moore that the number of transistors on a chip tends to double roughly every eighteen months. In recent years, following that trend has become increasingly complex: the ever-shrinking size of the components and the distance between them makes manufacturing difficult, while interference between components must be corrected and designed out.

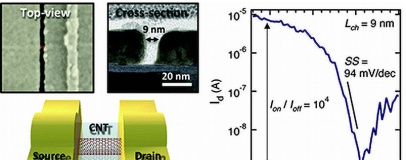

One possible solution is a move away from traditional semiconductor designs, and numerous companies are working on exactly that. Back in 2012, IBM announced the creation of a 9nm carbon nanotube resistor, dropping below the 10nm barrier for the first time. In September last year, the company further announced that it had used the transistors to build a fully working computer for the first time, but the company was still silent as to when the technology would be likely to leave the lab and reach shop shelves.

Speaking to MIT's Technology Review, IBM researchers have finally given themselves a deadline: to have commercialised carbon nanotube transistor semiconductors by the early 2020s. The secret is a shift in design, featuring six nanotubes measuring 1.4nm in width lined up in parallel, to build the transistors. This design, the company has claimed, could potentially be manufactured using current semiconductor fabrication plants with little modification - the route-to-market the technology desperately needed.

There's still a long way to go before we'll be able to buy systems featuring the five-fold performance increase promised by IBM's carbon nanotube technology, however. The company's design currently requires that bulk-purchased nanotubes are filtered to find those which are suitable for use in transistors, a small percentage of the overall batch, and the overall size of the finished transistor - six 1.4nm nanotubes with 8nm gaps between for a width of 48.4nm and a length of around 30nm in total - is still far too large to compete with the 14nm-and-shrinking size of traditional transistors.

The semiconductor industry has been working hard for the last few decades on following Moore's Law, the observation by Intel co-founder Gordon Moore that the number of transistors on a chip tends to double roughly every eighteen months. In recent years, following that trend has become increasingly complex: the ever-shrinking size of the components and the distance between them makes manufacturing difficult, while interference between components must be corrected and designed out.

One possible solution is a move away from traditional semiconductor designs, and numerous companies are working on exactly that. Back in 2012, IBM announced the creation of a 9nm carbon nanotube resistor, dropping below the 10nm barrier for the first time. In September last year, the company further announced that it had used the transistors to build a fully working computer for the first time, but the company was still silent as to when the technology would be likely to leave the lab and reach shop shelves.

Speaking to MIT's Technology Review, IBM researchers have finally given themselves a deadline: to have commercialised carbon nanotube transistor semiconductors by the early 2020s. The secret is a shift in design, featuring six nanotubes measuring 1.4nm in width lined up in parallel, to build the transistors. This design, the company has claimed, could potentially be manufactured using current semiconductor fabrication plants with little modification - the route-to-market the technology desperately needed.

There's still a long way to go before we'll be able to buy systems featuring the five-fold performance increase promised by IBM's carbon nanotube technology, however. The company's design currently requires that bulk-purchased nanotubes are filtered to find those which are suitable for use in transistors, a small percentage of the overall batch, and the overall size of the finished transistor - six 1.4nm nanotubes with 8nm gaps between for a width of 48.4nm and a length of around 30nm in total - is still far too large to compete with the 14nm-and-shrinking size of traditional transistors.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.