AMD has revealed more details of its upcoming Zen-based supercomputer-centric processor, in a paper published with the Institute of Electrical and Electronics Engineers (IEEE).

Designed to turn around the struggling company's finances, news of AMD's next-generation 32-thread Zen accelerated processing unit (APU) leaked back in April. Promising 16 physical processing cores and support for 32 threads, the chips were claimed to be designed with high-performance computing (HPC) in mind with features like a 32MB shared L3 cache with Heterogeneous Systems Architecture (HSA) coherency, cryptographic co-processor, and Greenland embedded graphics with up to 16GB of high-bandwidth memory (HBM) running at 512GB/s.

The launch plan was confirmed in March when AMD revealed a roadmap which suggested the part would have a whopping 200-300W thermal design profile (TDP), and now a paper entitled Achieving Exascale Capabilities through Heterogeneous Computing published in the IEEE Micro journal has offered a few more details.

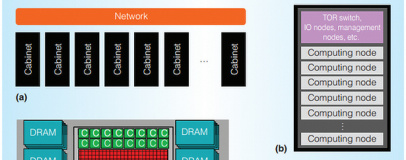

Spotted by Bits and Chips the paper confirms that the upcoming chip will be an APU in all but name, featuring a rebrand to Exascale Heterogeneous Processor (EHP) in order to appeal to the HPC crowd and distance itself from the mainstream APU parts which offer middling performance at best. A block diagram of 'an example exascale heterogeneous processor' included with the paper demonstrates the layout, confirming that the APU chip will be positioned on a silicon interposer with a large quantity of HBM2 DRAM and a connection to multiple modules of off-package non-volatile RAM (NVRAM).

AMd's vision, the paper explains, is to pack as many of these EHP modules as possible into a data centre: the diagram shows racks filled with computing nodes powered by the EHP part, with the network comprising of multiple cabinets in the usual cluster-style arrangement of high-performance computing systems.

'Exascale computing requires very high levels of performance capabilities while staying within very stringent power budgets. Hardware optimised for specific functions is much more energy efficient than implementing those functions with general purpose cores,' the abstract of AMD's paper explains. 'However, there is a strong desire for supercomputer customers to not have to pay for custom components designed only for high-end HPC systems, and therefore high-volume GPU technology becomes a natural choice for energy-efficient data-parallel computing. To fully realise the capabilities of the GPU, we envision exascale compute nodes comprised of integrated CPUs and GPUs (i.e., accelerated processing units or APUs) along with the hardware and software support to enable scientists to effectively run their scientific experiments on an exascale system.'

The EHP is expected to launch some time next year, for selected customers with deep pockets only.

Designed to turn around the struggling company's finances, news of AMD's next-generation 32-thread Zen accelerated processing unit (APU) leaked back in April. Promising 16 physical processing cores and support for 32 threads, the chips were claimed to be designed with high-performance computing (HPC) in mind with features like a 32MB shared L3 cache with Heterogeneous Systems Architecture (HSA) coherency, cryptographic co-processor, and Greenland embedded graphics with up to 16GB of high-bandwidth memory (HBM) running at 512GB/s.

The launch plan was confirmed in March when AMD revealed a roadmap which suggested the part would have a whopping 200-300W thermal design profile (TDP), and now a paper entitled Achieving Exascale Capabilities through Heterogeneous Computing published in the IEEE Micro journal has offered a few more details.

Spotted by Bits and Chips the paper confirms that the upcoming chip will be an APU in all but name, featuring a rebrand to Exascale Heterogeneous Processor (EHP) in order to appeal to the HPC crowd and distance itself from the mainstream APU parts which offer middling performance at best. A block diagram of 'an example exascale heterogeneous processor' included with the paper demonstrates the layout, confirming that the APU chip will be positioned on a silicon interposer with a large quantity of HBM2 DRAM and a connection to multiple modules of off-package non-volatile RAM (NVRAM).

AMd's vision, the paper explains, is to pack as many of these EHP modules as possible into a data centre: the diagram shows racks filled with computing nodes powered by the EHP part, with the network comprising of multiple cabinets in the usual cluster-style arrangement of high-performance computing systems.

'Exascale computing requires very high levels of performance capabilities while staying within very stringent power budgets. Hardware optimised for specific functions is much more energy efficient than implementing those functions with general purpose cores,' the abstract of AMD's paper explains. 'However, there is a strong desire for supercomputer customers to not have to pay for custom components designed only for high-end HPC systems, and therefore high-volume GPU technology becomes a natural choice for energy-efficient data-parallel computing. To fully realise the capabilities of the GPU, we envision exascale compute nodes comprised of integrated CPUs and GPUs (i.e., accelerated processing units or APUs) along with the hardware and software support to enable scientists to effectively run their scientific experiments on an exascale system.'

The EHP is expected to launch some time next year, for selected customers with deep pockets only.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.