AMD downplays 29 percent Zen 2 IPC boost reports

November 14, 2018 | 10:13

Companies: #amd #taiwan-semiconductor

AMD has issued a statement to address media reports that its upcoming Zen 2 microarchitecture could offer a 29 percent performance uplift over previous-generation Zen parts, clarifying that the figure quoted by the media is related to a very specific workload only and should not be taken as a general improvement in instructions per clock (IPC).

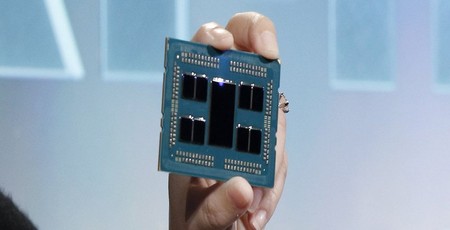

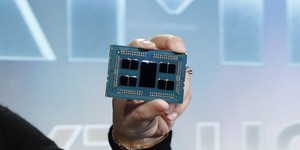

AMD chief executive Dr. Lisa Su formally unveiled Zen 2 at a press event last week, in which the microarchitecture was promised to launch on a 7nm process node from Taiwan Semiconductor and would first arrive in server-centric Epyc processors which combine multiple 7nm CPU 'chiplets' - offering up to 64 cores and 128 logical threads per processor - and a single 14nm input/output 'chiplet'. The unveiling came with the promise of numerous improvements over previous-generation microarchitectures, including tweaks in instructions per clock (IPC) - but some media outlets took one particular claim rather more generally than should have been the case.

In media material shared to boost anticipation for the new chips, codenamed Rome, AMD pointed to the result of a benchmark which saw a 29 percent performance improvement clock-for-clock over last-generation Zen parts. This was widely reported as proving a 29 percent improvement in IPC, but AMD has quickly announced that no such massive general improvement should be expected - though IPC is, indeed, improved. 'As we demonstrated at our Next Horizon event last week, our next-generation AMD Epyc server processor based on the new "Zen 2" core delivers significant performance improvements as a result of both architectural advances and 7nm process technology,' AMD has clarified in a statement to press. 'Some news media interpreted a "Zen 2" comment in the press release footnotes to be a specific IPC uplift claim.

'The data in the footnote represented the performance improvement in a microbenchmark for a specific financial services workload which benefits from both integer and floating point performance improvements and is not intended to quantify the IPC increase a user should expect to see across a wide range of applications,' AMD's clarification continues. 'We will provide additional details on "Zen 2" IPC improvements, and more importantly how the combination of our next-generation architecture and advanced 7nm process technology deliver more performance per socket, when the products launch.'

AMD's Rome chips have begun sampling to customers, but the company is so far silent on general availability; the company has also not released actual benchmark results, nor allowed any of its customers to do so, which doubtless contributed to the confusion.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.